My logicly integrated circuit pack contains a 8*256 RAM,but if I try to pull this to the circuit area,the logicly crashes(cuz of no memory or computational time to use cuz of that ram)

How can I solve that?

Inside brain

Hmm...

I don't think this has any relation to the Snap! editor

but seriously, why would you remove RAM in your computer?

...

I mean Logic.ly

which is a circuit design program

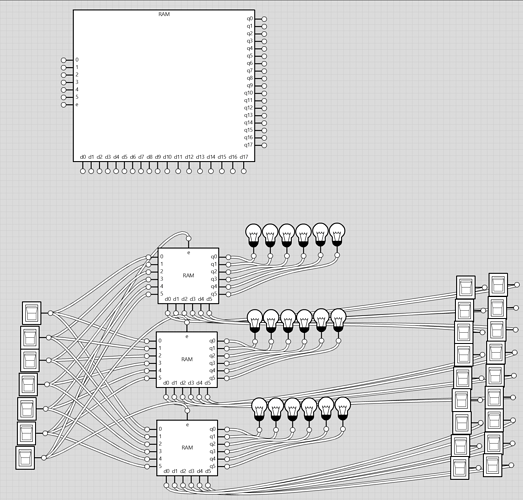

and i made a ram in it

haha lol but i had to ask it somewhere

Made it 1864 instead of 24256 so its now that laggy now

now its big

why 18*64 instead of 8*64?

Because I designed every instruction to accept 3 inputs,which is

a-=b

if(negative flag in ALU)set instruction register to c,clear alu flags

This way we dont need opcodes and just need to execute this instruction sequentially on every clock cycle

So every instruction consists of 3 addresses.

If we have 256 bytes of memory,each byte is 24 bits long.

If we have a gigabyte of memory each byte is 90 bits long.

If we have 64 bytes of memory each byte is 18 bits long.

oooohhh

That's interesting...

I've never seen this before, but if you have luck. you can get in contact with the associated program developer...

uh ill try another circuit diagram maker

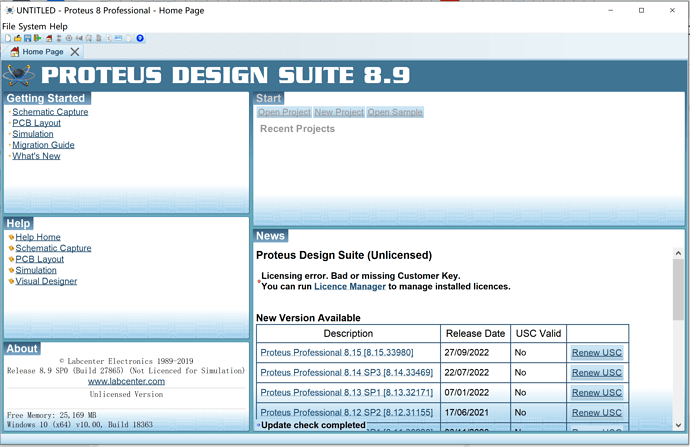

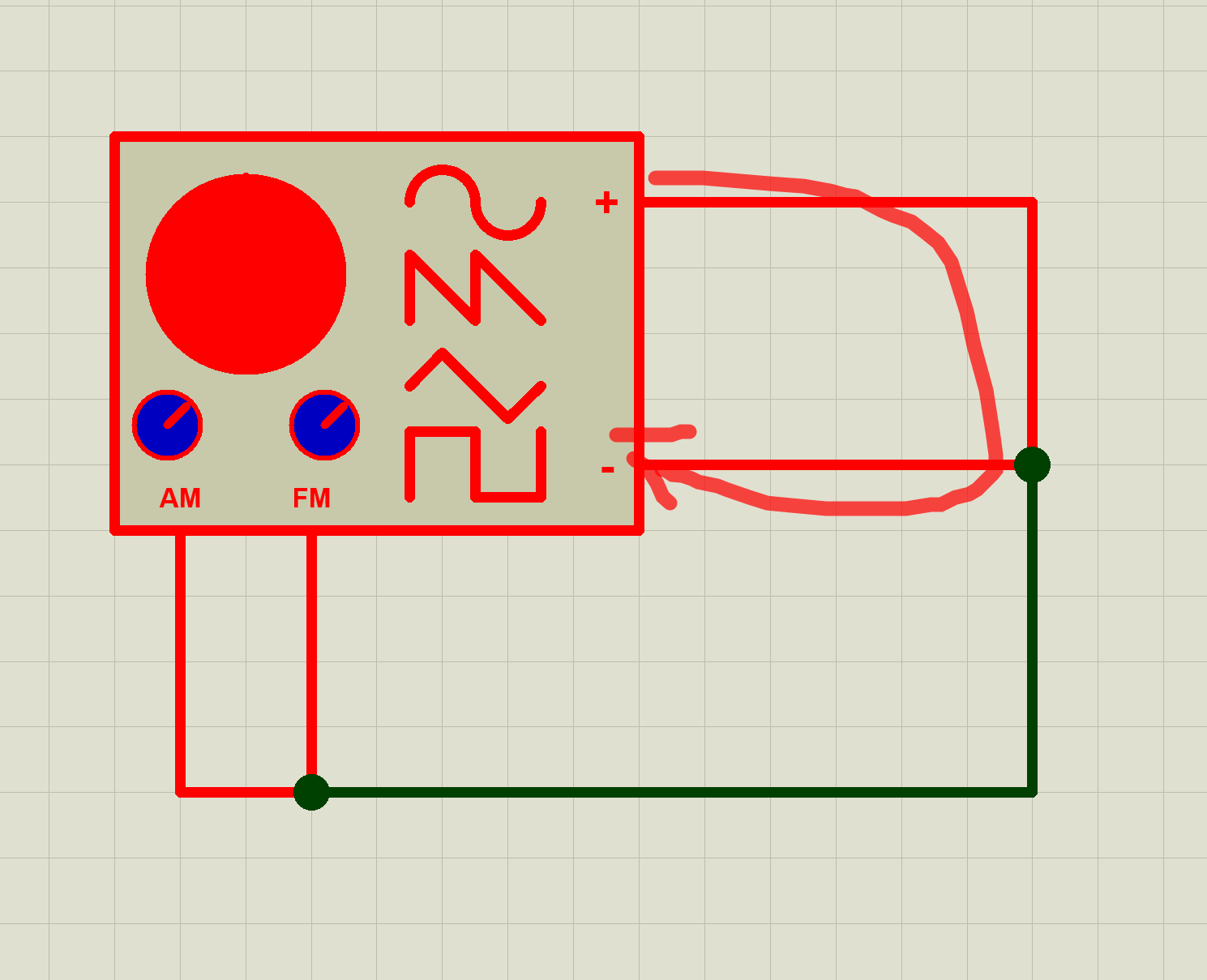

Got a cracked proteus

looks gud

looks not laggy

wait was that a key that expired at 2020?

Fixed!(the software wants me to use it for 7 years and 2 months C:)

ahahahahha

o i c but now i find out i cant toggle wires in the circuit

This topic was automatically closed 30 days after the last reply. New replies are no longer allowed.